The HD44780 is a character LCD controller developed by HITACHI during the 1980s. So fa it still a popular stuff for electronics hobbyists, especially the Arduino user. The micro-processor should interface with this LCD using its 8-bit data bus mode. But using the 4-bit data bus mode is common for most electronics designers.

|

| Hardware Test on the XC95108 Prototype Board |

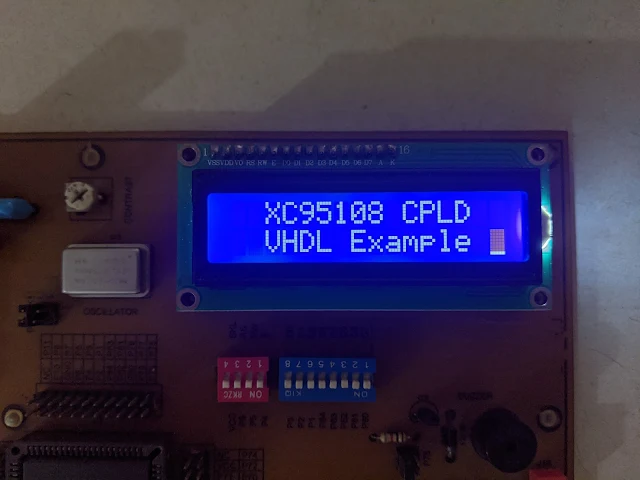

A digital circuit also able to control this LCD module using a state machine model. If you are a beginner in digital electronics design you can see this post. In this VHLD example, I use an XC95108 CPLD to interface with this LCD controller using the 8-bit data transfer mode. The LCD is a 16x2 character LCD. It will show text on both lines of the LCD. The text should be "XC95108 CPLD" on the first line, and "VHDL Example" on the second line.

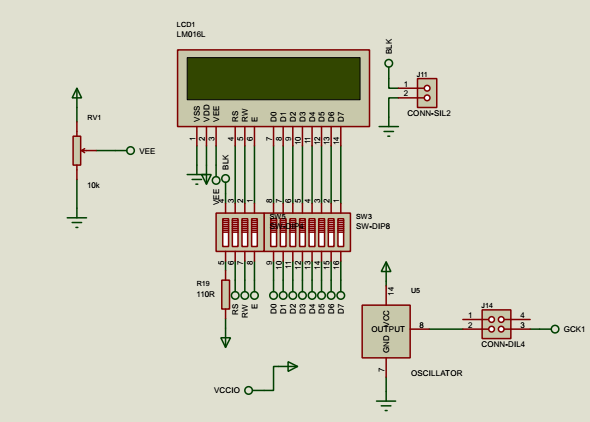

The on-board oscillator is 25.175MHz. So I need to add a VHDL clock divider circuit to get a 1kHz signal.

|

| The on-board oscillator is 25.175MHz |

Data or command are latched into the LCD controller from logic high low. So at the high logic level the circuit starts send data or command to the LCD. Then they will be latched into the LCD at the up coming logic low.

|

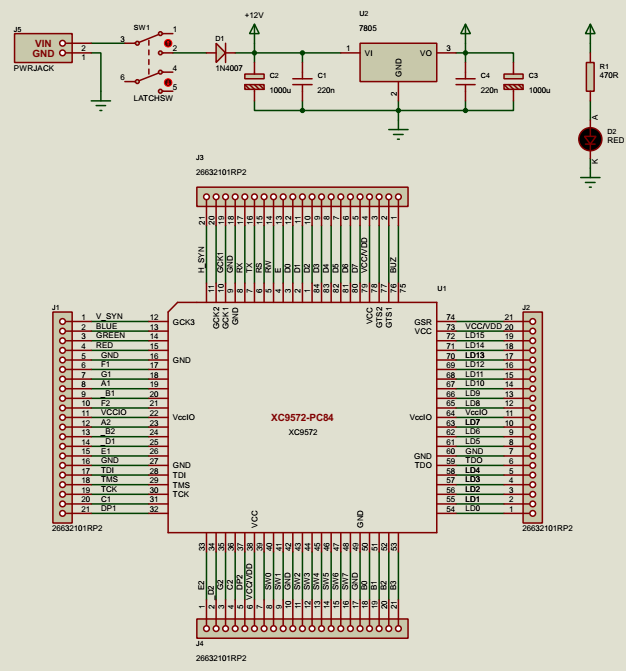

| Main CPLD Prototype Board Block |

|

| Character LCD and Oscillator |

#PACE: Start of Constraints generated by PACE

#PACE: Start of PACE I/O Pin Assignments

NET "CLK" LOC = "P9" ;

NET "DB<0>" LOC = "P2" ;

NET "DB<1>" LOC = "P1" ;

NET "DB<2>" LOC = "P84" ;

NET "DB<3>" LOC = "P83" ;

NET "DB<4>" LOC = "P82" ;

NET "DB<5>" LOC = "P81" ;

NET "DB<6>" LOC = "P80" ;

NET "DB<7>" LOC = "P79" ;

NET "EN" LOC = "P3" ;

NET "RS" LOC = "P5" ;

NET "RST" LOC = "P40" ;

NET "RW" LOC = "P4" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

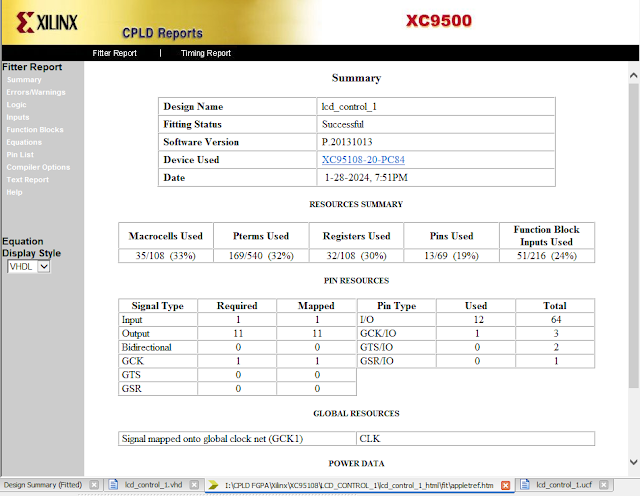

This digital circuit design uses 35 macro cells and 51 Function Block.

|

| XC95108 CPLD Reports |

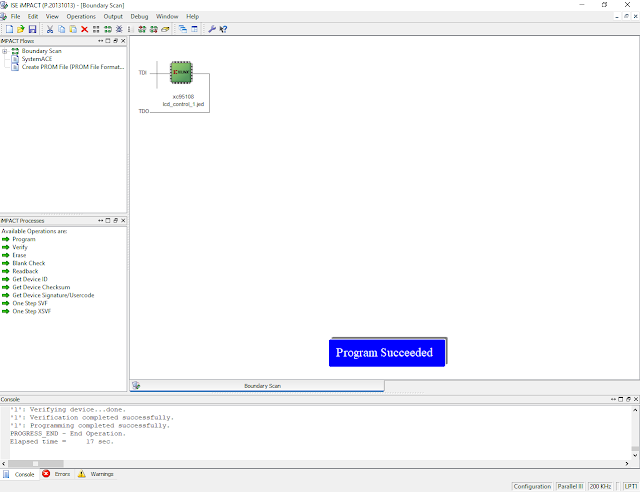

Using a Xilinx Parallel Cable III or IV is suitable for device programming in the Xilinx ISE Design Suite 14.7.

|

| Device Programming Using a Xilinx Parallel Cable IV JTAG |

Click here to download its source file.

No comments:

Post a Comment