Character LCD interfacing is very popular among electronics hobbyists. Using a minimum 8-bit microcontroller with Assembly language programming is very common. This simple 8-bit HD44780 character LCD can be tested manually by applying digital logic inputs by switches without using any controller.

Some electronics practitioners use a digital circuit created by some digital logic chips to control this character LCD. Similarly a Programmable Logic Device (PLD) can replace that complex digital electronics circuit. We can use schematic design or even an easier VHDL or Verilog coding to design an LCD interface circuit that will run on any CPLD or FPGA.

|

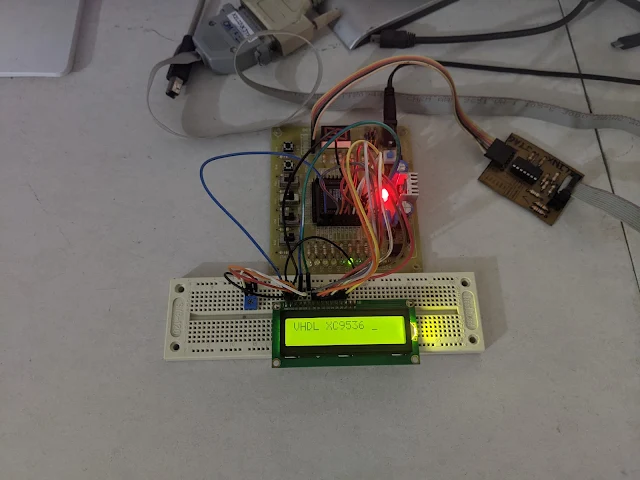

| VHDL Code Testing on an experiment board |

In this VHDL example, I use an old simple Complex Programmable Logic Device (CPLD) to create a digital electronics circuit inside to interface with a HD44780 based character LCD module.

Using a Finite State Machine (FSM) model is very common this task. However I didn't follow all of this FSM model. I use a counter to activate each steps of data transfer between CPLD and LCD module.

An on-board 60Hz square wave oscillator is needed to active the circuit. LCD data and command are sequentially send to the LCD. It activated only at the high logic level of Enable (EN) output pin.

I use a low cost Chinese JHD162A LCD module. It costs around 2USD at local store.

|

| JHD162A LCD Module Interfacing Pins |

The following VHDL codes will show a "VHDL XC9536" message on a character LCD. Then it will stop transferring data.

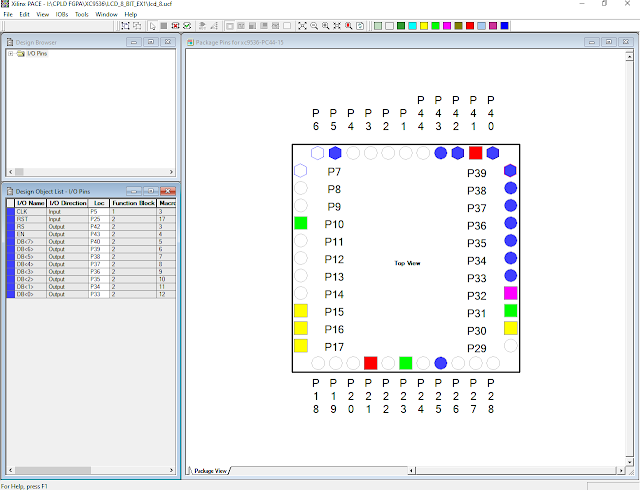

Don't forget to assign its I/O pins. The LCD 8-bit data bus shares with on-board LEDs.

|

| Xilinx PACE Tool - I/O Pin Assignments |

We will need to run the Implement Design again to wire its I/O pins. We will see its CPLD Reports.

|

| CPLD Reports |

If you have a Desktop computer with a legacy parallel port we can use a Xilinx Parallel Cable III JTAG to program this CPLD. However a modern USB JTAG is currently widely used with an affordable price. A USB JTAG cable is very stable to use than a legacy one's.

Click here to download its VHDL, UCF, and JED files.

No comments:

Post a Comment