In this VHDL example, I use an XC85108 CPLD to read an 8-bit binary input. Then the internal digital circuit will convert it into hexadecimal value. The result is in 2 place values hexadecimal displaying on a two-digit common cathode 7-Segment display.

|

| XC95108 CPLD DIY Prototype Board |

I divided the 8-bit input into two nibble, the higher nibble and the lower nibble. The VHDL conversion between these two bases is very straight forward. The code just decode these two nibble using the concurrent VHDL WITH and Select statement.

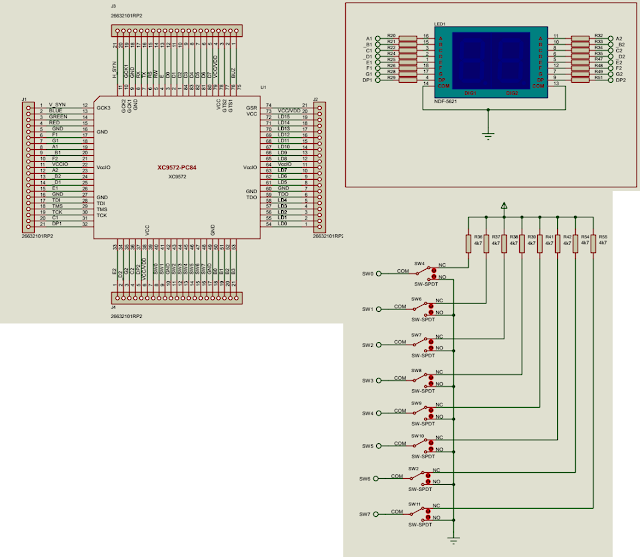

The XC95108, 7-Segment display and input switch wiring diagram are listed below.

|

| Wiring Diagram on the XC95108 CPLD Prototype Board |

In Xilinx ISE we need to assign its I/O pins using Floorplan IO tool.

|

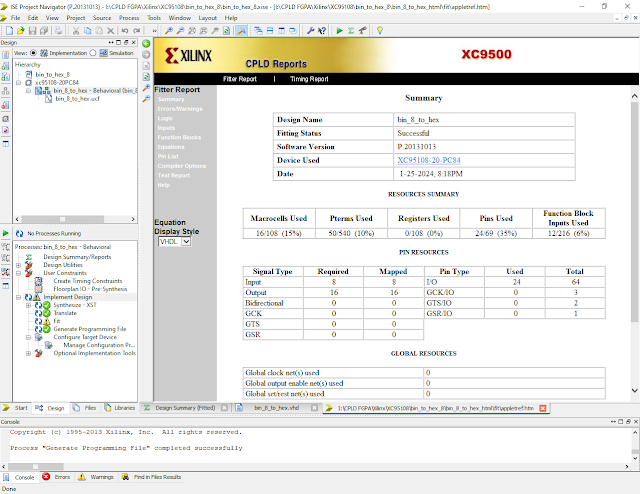

| XC9500 CPLD Report |

This digital circuit design requires very little resource of the XC95108 CPLD. We can use the Xilinx Parallel Cable III to program this CPLD in Xilinx ISE 14.7.

Click here to download this example.

No comments:

Post a Comment