In previous post, I use the XC95108 to make a 16-bit LED shift registers. It's similar to the SNHC164 serial in parallel out shift registers chip. Using a CPLD and VHDL code we can customize any digital circuit.

|

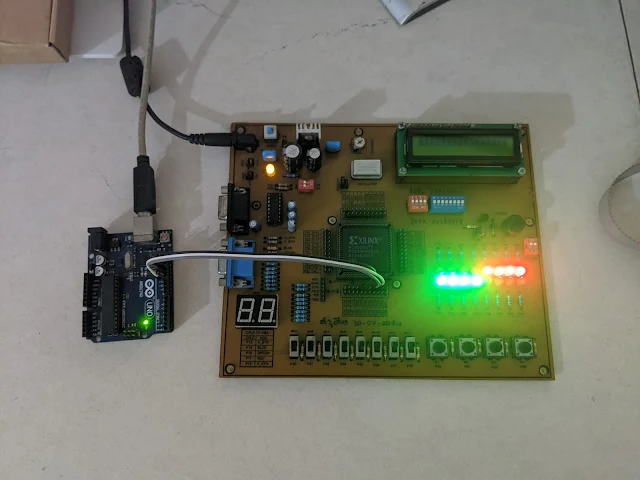

| The Arduino Uno and the XC95108 CPLD Prototype Board |

Here I make another serial in parallel out shift registers chip that's similar to the SN74HC595. It's a two-digit 7-Segment display driver with SPI interface. It has the following I/O:

- Reset (RST) input (active low)

- Enable (EN) input for data latching

- Serial Data In (MOSI)

- Serial Clock In (SCK)

- 7-Segment Digit 1 (LEDA)

- and 7-Segment Digit 2 (LEDB).

The 7-Segment display is a two-digit 0.56" red common cathode display. The shift registers process is synchronize with the logic high level of serial clock input (SCK). Shift registers data are latched into the output LED ports at the high to low transition of the EN (Enable) pin.

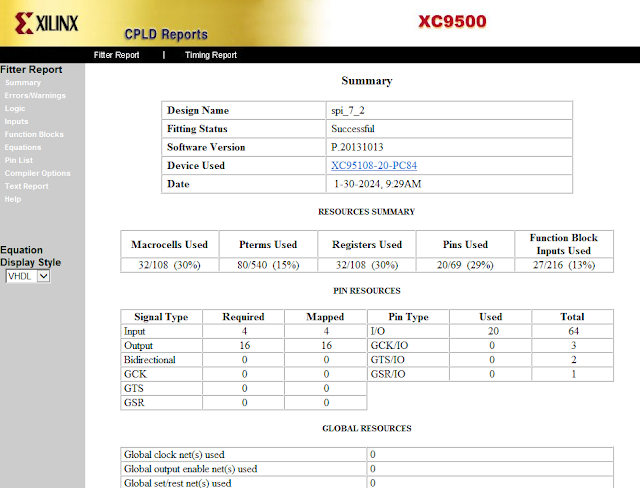

This VHDL circuit design uses 32 macro cells and 27 function blocks.

|

| XC95108 CPLD Reports |

I connect the CPLD to its on-board I/O devices (user constraint file) as follow.

Using the Arduino Uno is common for most of electronics hobbyists. I use the Arduino SPI to send 7-Segment data to the XC95108 CPLD Prototype Board. This program will count up and down between 0 and 99.

The Arduino Uno must connects to the CPLD as follow.

- Arduino Uno GND -> XC95108 CPLD GND

- Arduino Uno SCK (PIN13) -> XC95108 CPLD (P52)

- Arduino Uno MOSI (PIN11) -> XC95108 CPLD (P53)

- Arduino Uno EN (PIN10) -> XC95108 CPLD (P54)

Click here to download its source file.