The XC95108 is a high-performance CPLD providing advanced in-system programming and test capabilities for general purpose logic integration. It is comprised of six 36V18 Function Blocks, providing 2,400 usable gates with propagation delays of 7.5 ns. It has a 5V in-system programmable (ISP) that allow us to program/erase up to 10000 cycles.

|

| The XC9572 XC95108 Prototype Board |

|

| XC95108 Architecture |

We can design the circuit using schematic tool, VHLD, or Verilog using Xilinx ISE. The ISP tool could be a legacy parallel port cable (II) or even a modern USB JTAG.

In this introductory example, I design a frequency divider circuit using VHDL. The frequency source is driven from a 25.175MHz crystal oscillator. The output frequency is 1Hz that will drive an output LED.

I use VHDL Generic to parameterize the design, conferring the code more flexibility and flexibility.

This VHDL code could fit an XC9572 CPLD. But this chip is not currently available at my workshop.

|

| XC95108 PLCC-84 |

I use an XC95108 PC84 (PLCC-84) with socket. Its speed grade is 20 Nano seconds.

|

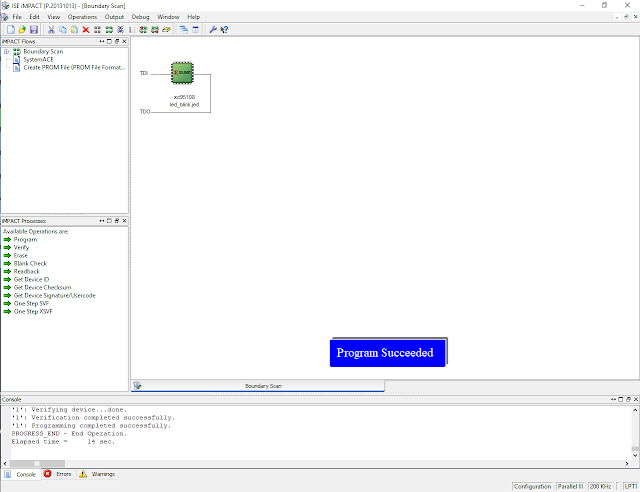

| Xilinx Impact ISP |

I still use the Xilinx Parallel Cable III to program this old CPLD. Its operating speed is slower than a modern USB JTAG.

Click here to download this VHDL example.

No comments:

Post a Comment