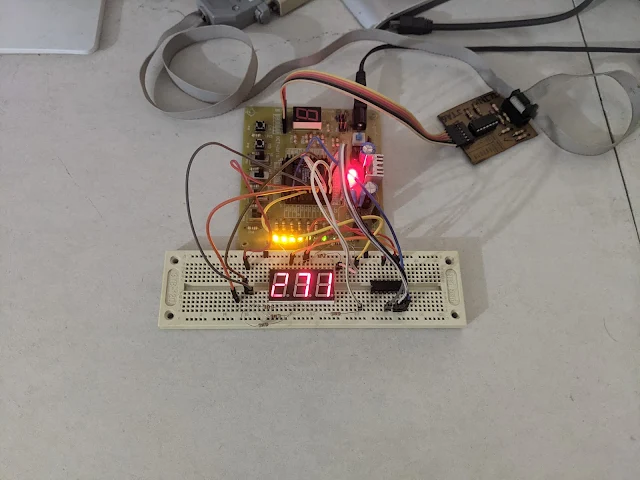

In this VHDL Example, an XC9536 CPLD will drive a three-digit common cathode multiplexing display. Each digits represent individual counting value ranges from 0 to 9 decimal values. A larger CPLD can create a 0 to 999 digital counters but this small XC9536 CPLD run out of resource. So I just design an individual digit counters.

|

| Running Circuit on an XC9536 CPLD Prototyping Board |

This digital circuit design contains only on sequential process activates by input clock and reset signal.

Multiplexing display processed by the VHDL WHEN statement. Each input counting buttons are also place inside the WHEN statement because they require a longer period to be activated. So it reduce switch bouncing.

|

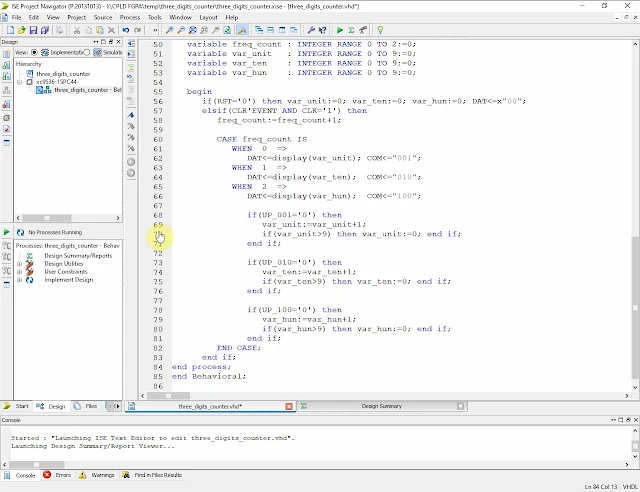

| Source Code Windows |

I assigned its I/O pins as follow.

|

| Xilinx PACE |

Click save and close this windows a user constraints file will automatically generated by software.

#PACE: Start of PACE I/O Pin Assignments

NET "CLK" LOC = "P5" ;

NET "COM<0>" LOC = "P42" ;

NET "COM<1>" LOC = "P43" ;

NET "COM<2>" LOC = "P44" ;

NET "DAT<0>" LOC = "P33" ;

NET "DAT<1>" LOC = "P34" ;

NET "DAT<2>" LOC = "P35" ;

NET "DAT<3>" LOC = "P36" ;

NET "DAT<4>" LOC = "P37" ;

NET "DAT<5>" LOC = "P38" ;

NET "DAT<6>" LOC = "P39" ;

NET "DAT<7>" LOC = "P40" ;

NET "RST" LOC = "P26" ;

NET "UP_001" LOC = "P18" ;

NET "UP_010" LOC = "P19" ;

NET "UP_100" LOC = "P25" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

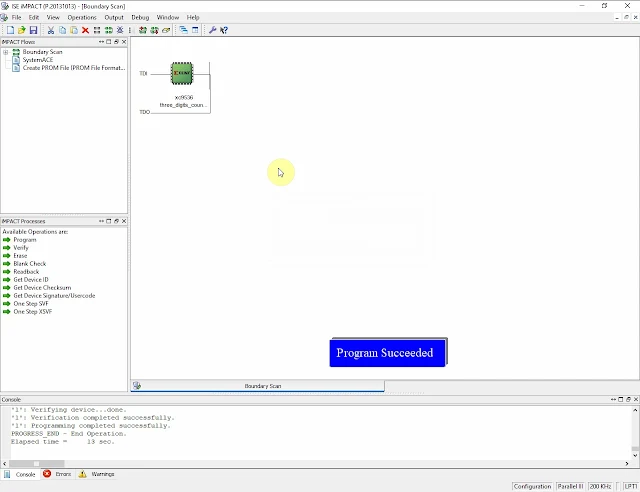

An Xilinx Parallel Cable III still useable in Xilinx ISE Design Suites 14.7.

|

| CPLD Reports |

|

| Xilinx Parallel Cable III JTAG Programming for XC9536 CPLD |

If you are new to VHDL and Xilinx ISE Design Tool you can watch this video on YouTube.

Click here to download its source file.

No comments:

Post a Comment