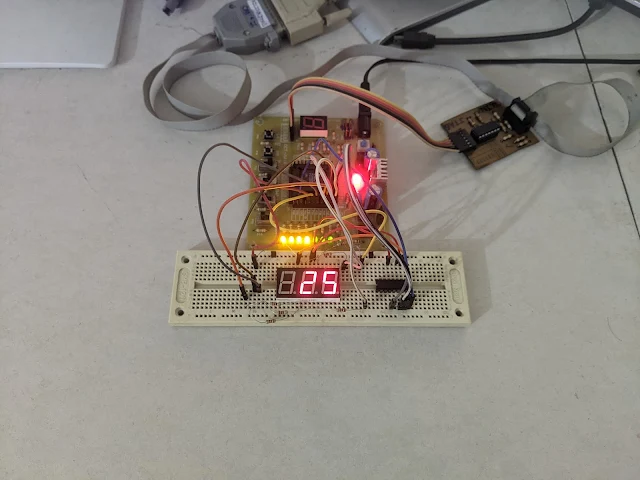

In this VHDL example, I use a Xilinx XC9536 CPLD to create a digital up counter with a two-digit multiplexing seven-segment display. This counter will count up to 99 before it rolls down to 0. This CPLD has limited resource so we can not create more digits or temporary variable to process this circuit, even a three-digit digital up counter.

|

| XC9536 CPLD Hardware Experiment |

In this design there are three inputs, clock, reset, and count push button. Clock signal is activated from low to high transition while reset and count signal are active low signals.

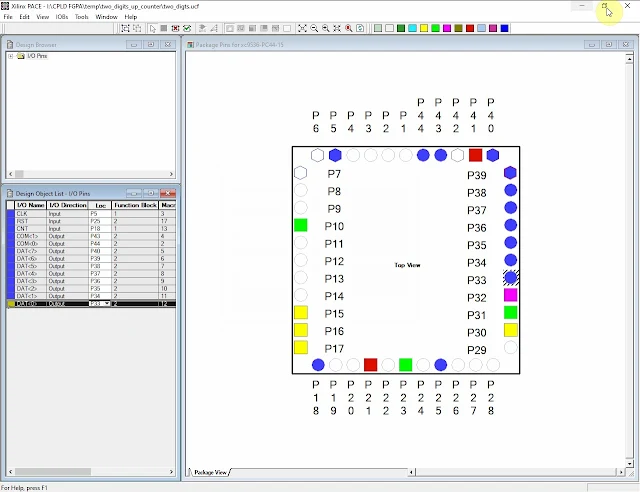

After the design implementation this circuit consume a lot of the SX9536's resource. So we can not add more features into this design. I assigned its I/O pins using Xilinx PACE as follow.

|

| Xilinx PACE |

Its generated user constraint file listed below.

#PACE: Start of PACE I/O Pin Assignments

NET "CLK" LOC = "P5" ;

NET "CNT" LOC = "P18" ;

NET "COM<0>" LOC = "P44" ;

NET "COM<1>" LOC = "P43" ;

NET "DAT<0>" LOC = "P33" ;

NET "DAT<2>" LOC = "P35" ;

NET "DAT<3>" LOC = "P36" ;

NET "DAT<4>" LOC = "P37" ;

NET "DAT<5>" LOC = "P38" ;

NET "DAT<6>" LOC = "P39" ;

NET "DAT<7>" LOC = "P40" ;

NET "RST" LOC = "P25" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

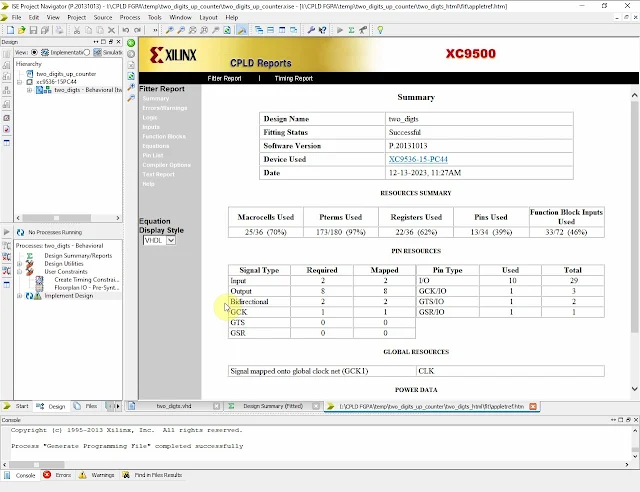

Then we will need to run the Implement Design again to get its programming file.

|

| CPLD Reports |

After the Implement Design is finished we can see the reports.

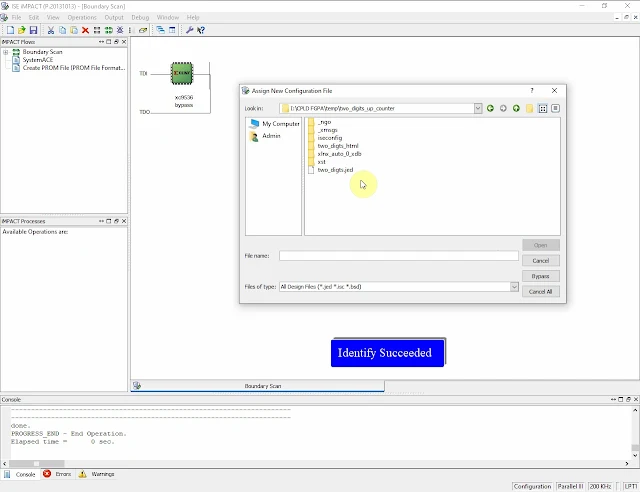

I still use Parallel Cable III in iMPACT tool to program this device.

|

| Xilinx iMPACT |

Click here to download its source file.

No comments:

Post a Comment