Overview

In this VHDL example, I use an input push button to toggle an output LED. It also has a delay circuit that created by frequency divider. Signal source is generated by the on-board 60Hz NE555 square wave oscillator.

|

| On-Board Testing |

In VHDL It requires two I/O pin,

- LED - Output direction with STD_LOGIC type. It's assigned to pin 35 of XC9536 CPLD, connecting the on-board output LED.

- CLK - Input direction with STD_LOGIC type. It's assigned to pin 5 (GCK1) of XC9536 CPLD.

- BUTTON : Input direction STD_LOGIC type. It's assigned to pin 19, connecting to the on-board pulled up tactile switch. It's an active low signal.

A counter variable "count" holds a numeric value up to 60 counts. It's necessary for sequential circuit inside the process. A toggle signal with STD_LOGIC type is added for signal assignment to LED I/O pin. When a low to high clock pulse is activated at clock pin (CLK) it increases its content 1 time. Whenever it reaches 30 counts and the the input button "BUTTON" is pressed, it will be reset to 0. And the toggle signal will change its logic state. The LED logic state depends on the toggle signal.

VHDL Code

The VHDL code contains a dozen line of statements. Only one process evaluates the input and output. This process requires one sensitive parameter "CLK" in its list.

Click here to download its source file. I want to know its RTL(Register Transfer Level) schematic.

|

| Register Transfer Level (RTL) |

User Constraints

I don't use VHDL simulation here. This circuit will be constructed on an XC9536 CPLD using my test board. So I need to select the I/O pins before the program file is uploaded to CPLD.

Expand the User Constraints, and double click on the Floorplan IO to assign its I/O pins. And then save the document before we close it.

|

| I/O Pins Assignment |

A user constraints file ".ucf" will be generated.

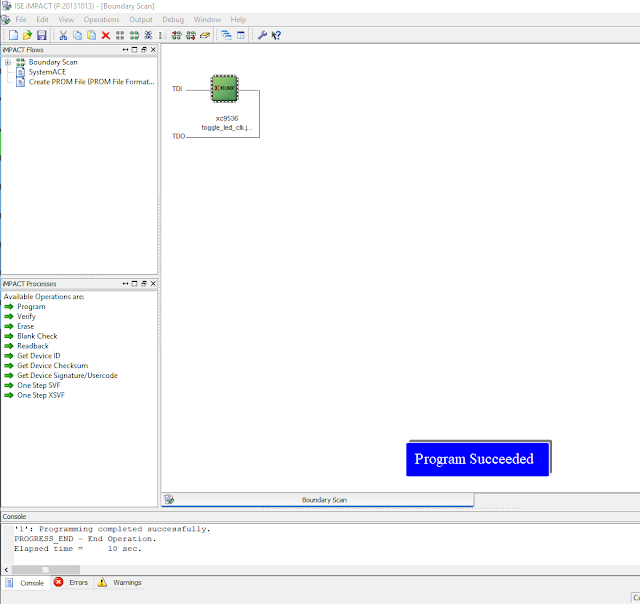

After it's completed, we need to run the Implement Design to generated its program file ".jed". This file will be selected to program the target CPLD device.

|

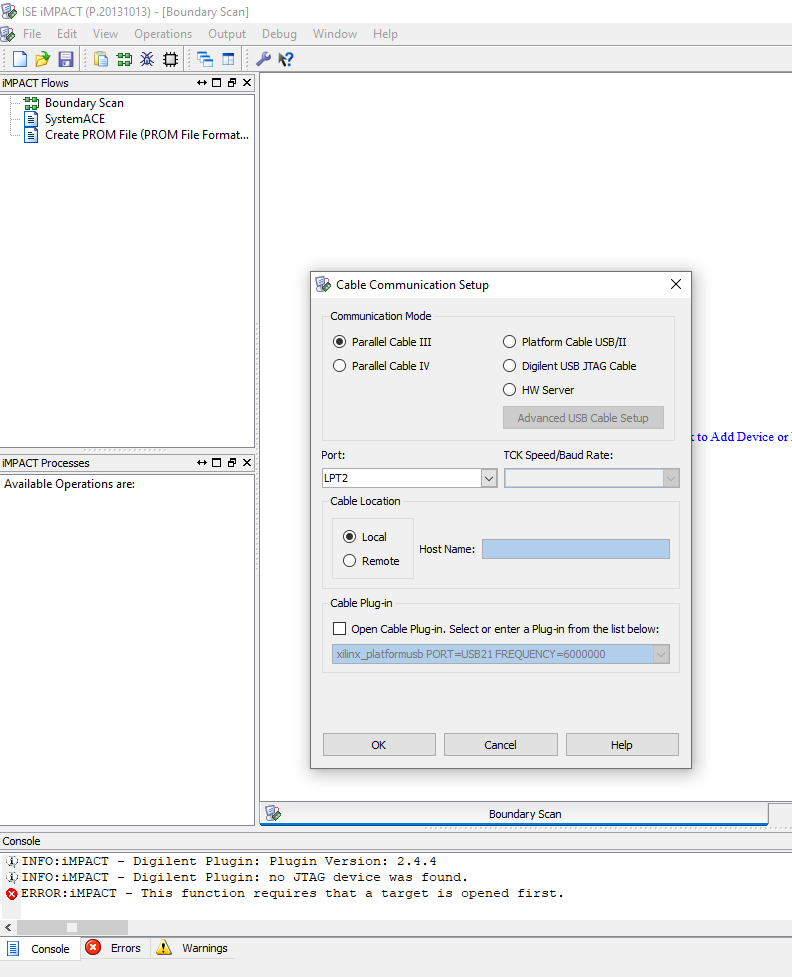

| Cable Set Up - Select Parallel Cable III |

I use the legacy parallel port interface connects to Parallel Cable III JTAG cable to program the target device. I use ISE Design Suites 14.7 running on Windows 10. My HP MT-6300 Desktop PC with parallel port still support this legacy I/O port. If you need a modern high speed USB JTAG, it works better than this old one's.

|

| Programming |

Using this parallel port cable we need to be patient because of its low speed, and cable connection error.

No comments:

Post a Comment