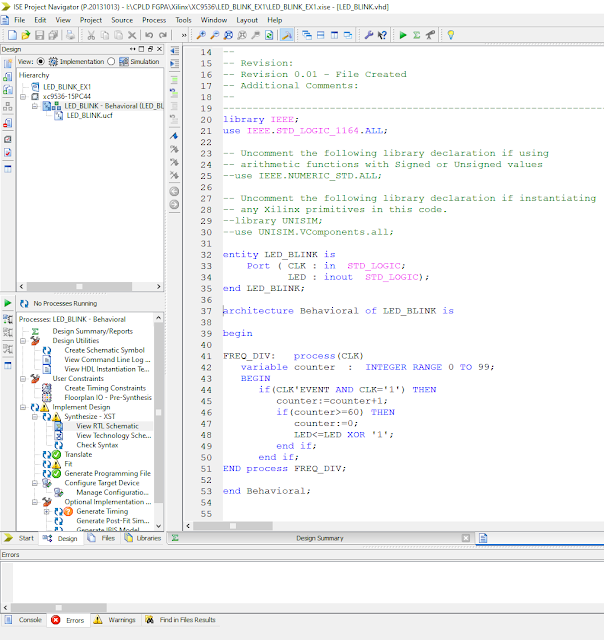

In this introductory VHDL coding, I use frequency divider to make a 1 second pulse duration. That pulse will drive and output LED high and low. I use an obsoleted part XC9536 CPLD manufactured by Xilinx. It was released in early 2000s. At that time we only requires a DIY legacy parallel port JTAG to program this Flash-based CPLD.

|

| XC9536 Test Board |

Clock source is fed by a NE555 oscillator circuit with a frequency of 60Hz. I use a sequential process block to count clock pulse, and LED controlling. A counter variable store, and increase counting value. Whenever it reaches 60 counts it will rolls back to 0. The output LED will toggle its logic state.

I add a User Constraints File (*.ucf) file for CPLD I/O assignment.

#PACE: Start of PACE I/O Pin Assignments

NET "CLK" LOC = "P5" ;

NET "LED" LOC = "P40" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

Without simulation in iSIM, I use ISE Impact to program the XC9536 CPLD. I use Xilinx ISE Design Suite 14.7 (nt64) on Microsoft Windows 10.

|

| Xilinx ISE Design 14.7 |

|

| Xilinx ISE Design Suite 14.7 |

|

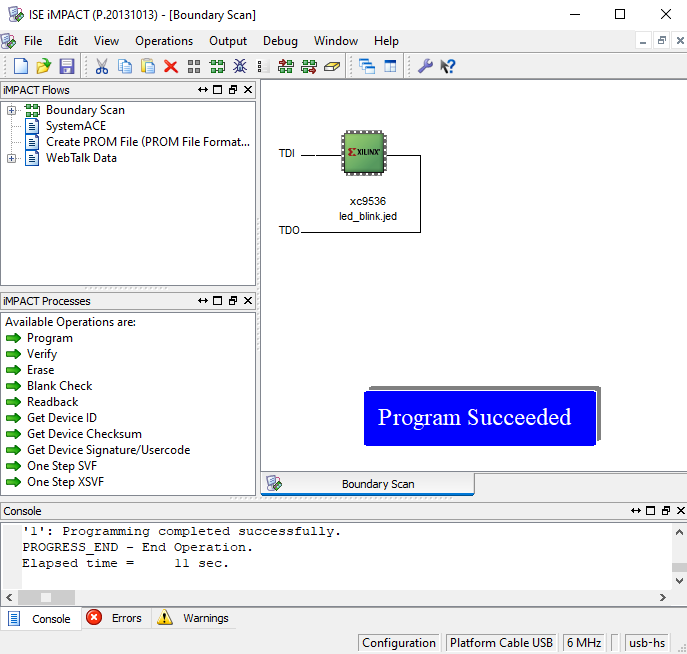

| ISE iMPACT With USB Platform Cable |

On Microsoft Windows 10, I use the Xilinx Platform USB Cable JTAG interface to program the target CPLD. Legacy parallel port JTAG cable was tested and it works find on Microsoft Windows 7 64-bit. However I have not yet test this legacy JTAG interface on Microsoft Windows 10.

|

| After JTAG Programmed |

Click here to download its source.

No comments:

Post a Comment