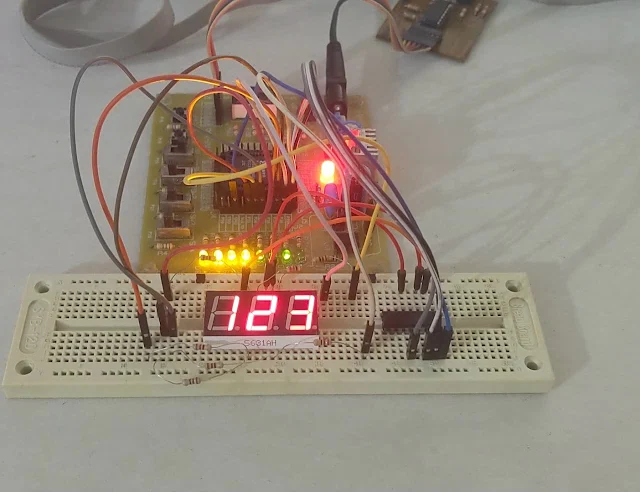

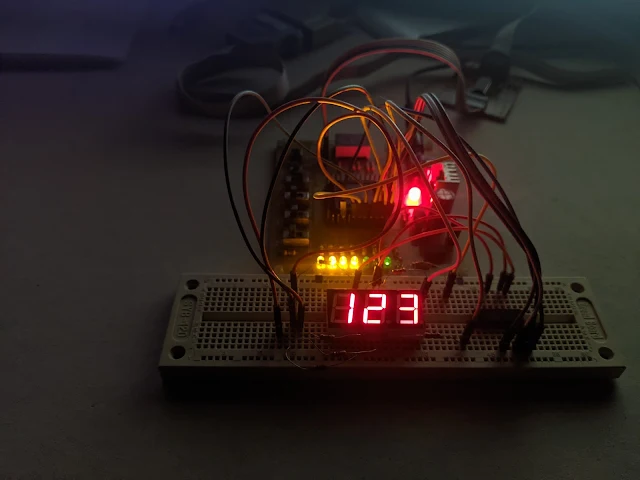

In this VHDL Example, an XC9536 CPLD drives a 3-digit common cathode multiplexing display. It requires a square signal generator for display timing. The generator frequency is 60Hz generated by an on-board NE555 square wave oscillator. Each digits are activated for 16 milliseconds.

|

| XC9536 Prototyping Board |

VHDL codes for this example is very simple. We directly assign 7-segment data to each digits. However we can use VHDL array data type.

All 7-Segment data pins share with the on-board output LEDs. So it reduce driving current. I use an ULN2003 transistors array to drive each common pins.

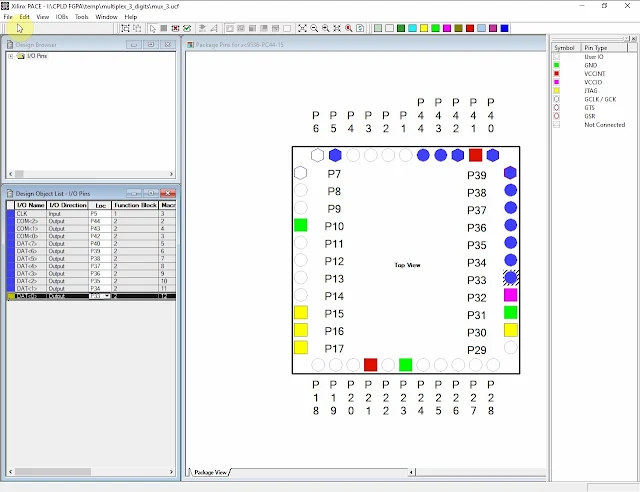

I assign all output pins in Xilinx PACE as follow.

|

| Pin Assignments |

Click here to download its source file.

If you are a beginner in VHDL you can watch this video to see the overall process.

No comments:

Post a Comment