Overview

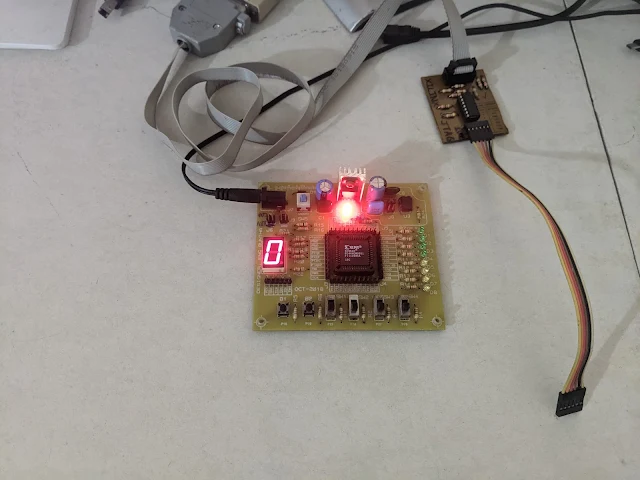

In this VHDL example, I use an XC9536 CPLD to read a 4-bit binary input. This input will translate to a hexadecimal value on a single common cathode 7-segment display. The XC9536 CPLD experiment board has four input slide switches, and eight output LEDs. So we don't need to use an additional bread board.

|

| when the binary input is "0000" |

The SELECT Statement

I use VHDL SELECT statement. It's a concurrent statement that's similar to the sequential statement CASE. The SELECT statement allows the use of multiple values (instead of multiple conditions). It requires that all input values be covered (complete truth table), for which the keyword OTHERS is often helpful. (Reference: Circuit Design With VHDL, Second Edition)

With BIN Select HEX <= "0111111" when "0000", -- 0 "0000110" when "0001", -- 1 "1011011" when "0010", -- 2 "1001111" when "0011", -- 3 "1100110" when "0100", -- 4 "1101101" when "0101", -- 5 "1111101" when "0110", -- 6 "0000111" when "0111", -- 7 "1111111" when "1000", -- 8 "1101111" when "1001", -- 9 "1110111" when "1010", -- A "1111100" when "1011", -- B "0111001" when "1100", -- C "1011110" when "1101", -- D "1111001" when "1110", -- E "1110001" when "1111", -- F "0000000" when OTHERS;

This design creates a concurrent circuit. That's not require of input clock.

VHDL Code

There are one 4-bit input, and one 7 bit output. The inputs read a digital value created by slide switches while the output connects to a single common cathode display. The display shows a hexadecimal value ranges from 0 to F.

We should try to compile this source code first before we assign the I/O on CPLD.

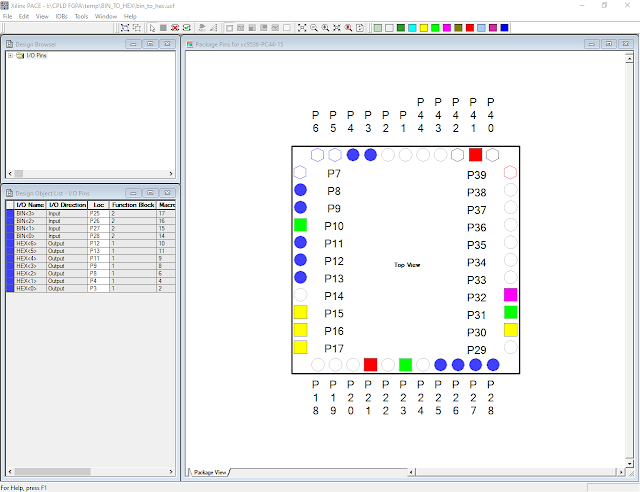

Pin Assignments

Under the User Constraints, double click on the Floorplan IO to open the Xilinx PACE tool.

|

| Pin Assignments |

After saving and close this window the ISE Design Suite will generate a user constraints ".ucf" file.

#PACE: Start of Constraints generated by PACE#PACE: Start of PACE I/O Pin Assignments

NET "BIN<0>" LOC = "P28" ;

NET "BIN<1>" LOC = "P27" ;

NET "BIN<2>" LOC = "P26" ;

NET "BIN<3>" LOC = "P25" ;

NET "HEX<0>" LOC = "P3" ;

NET "HEX<1>" LOC = "P4" ;

NET "HEX<2>" LOC = "P8" ;

NET "HEX<3>" LOC = "P9" ;

NET "HEX<4>" LOC = "P11" ;

NET "HEX<5>" LOC = "P13" ;

NET "HEX<6>" LOC = "P12" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

Click here to download its source file.

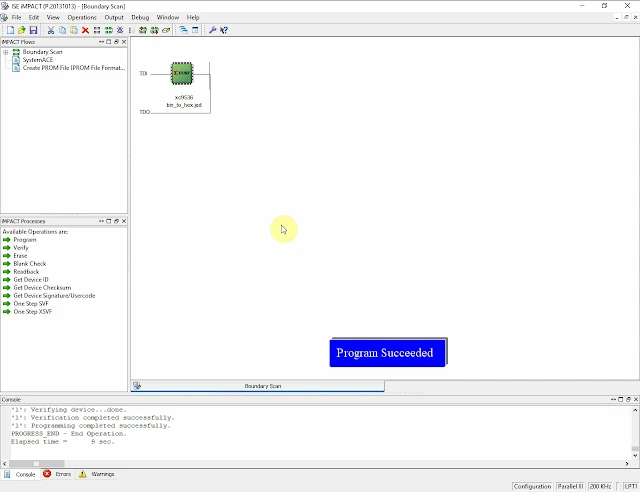

Programming the CPLD

After pin assignments is completed, we need to re-run the Implement Design. After it's finished we expand the Configure Target Device, and run the Manage Configuration Project (iMPACT).

|

| Xilinx iMPACT Tool |

The Parallel Cable III is useable under Microsoft Windows 10.

|

| Maximum Value |

The WHEN Statement

We can use VHDL WHEN statement to create this binary to hexadecimal converter. WHEN is the simplest conditional statement. It is approximately equivalent to the sequential statement IF. (Reference: Circuit Design With VHDL, Second Edition)

HEX <= "0111111" When BIN="0000" else -- 0 "0000110" When BIN="0001" else -- 1 "1011011" When BIN="0010" else -- 2 "1001111" When BIN="0011" else -- 3 "1100110" When BIN="0100" else -- 4 "1101101" When BIN="0101" else -- 5 "1111101" When BIN="0110" else -- 6 "0000111" When BIN="0111" else -- 7 "1111111" When BIN="1000" else -- 8 "1101111" When BIN="1001" else -- 9 "1110111" When BIN="1010" else -- A "1111100" When BIN="1011" else -- B "0111001" When BIN="1100" else -- C "1011110" When BIN="1101" else -- D "1111001" When BIN="1110" else -- E "1110001" When BIN="1111"; -- F

Its complete VHDL code is shown below.

The operating function using the SELECT statement.

|

| The WHEN Statement |

Click here to download its source code.

No comments:

Post a Comment