Overview

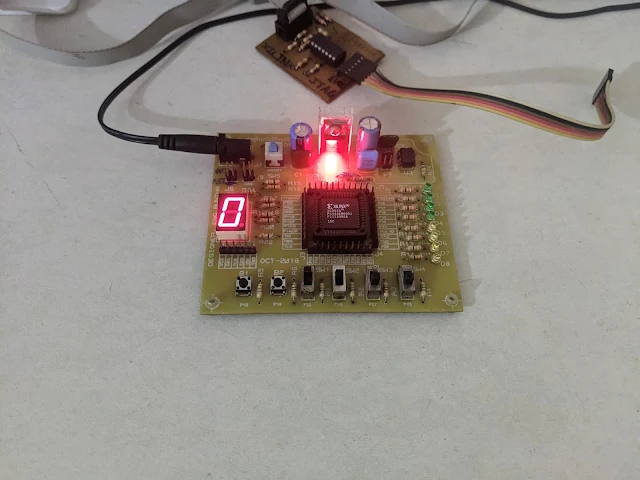

In this VHDL tutorial, I will design an up/down counter using VHDL code. Alternatively, we can use an ASIC 4516 and a 4511 chip to create this type of digital counter. However using a CPLD we can create and customize any digital circuit or ASIC by VHDL, Verilog code, or even schematic design tool.

|

| XC9536 CPLD Prototyping Board |

VHDL Code

Its source code is very simple to write, I use one sequential block (process). The IF statement to make a frequency division, and to test digital logic input's state change. Additionally, the CASE Statement is used for decoding the output seven segments data. I added one active low reset signal to zero all variables.

Up and Down logic input are active low. They are connected to pin 18 and 19 respectively. They are activated by pressing the buttons.

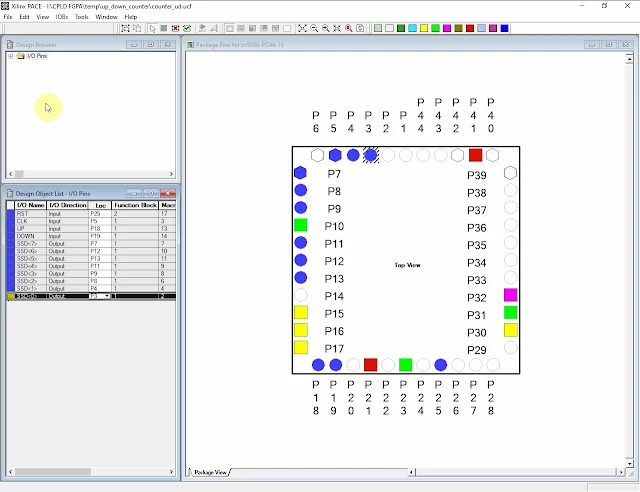

I/O Pin Assignments

I assign its I/O pins by using Xilinx PACE tool as follow.

|

| Pin Assignments |

A user constraints *.ucf file will be generated after we save the PACE.

NET "CLK" LOC = "P5" ;

NET "DOWN" LOC = "P19" ;

NET "RST" LOC = "P25" ;

NET "SSD<0>" LOC = "P3" ;

NET "SSD<1>" LOC = "P4" ;

NET "SSD<2>" LOC = "P8" ;

NET "SSD<3>" LOC = "P9" ;

NET "SSD<4>" LOC = "P11" ;

NET "SSD<5>" LOC = "P13" ;

NET "SSD<7>" LOC = "P7" ;

NET "UP" LOC = "P18" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

We can also create this source file and write the codes manually. After this step is completed, we will need to re-run the Implement Design to obtain its programming file *.jed .

Device Programming

We just run the iMPACT tool to program the target XC9536 CPLD. A high speed USB JTAG is popular now. However I still use a legacy parallel port JTAG header. It still present in Xilinx ISE Design Suite 14.7, and Microsoft Windows 10. My HP MT-6300 Desktop PC has a legacy PCI Express parallel port (LPT-25) card.

|

| iMPACT Tool |

Its operating speed is suitable for a small programming file.

|

| Program Succeeded |

Click here to download its source file.

No comments:

Post a Comment